NVIDIA Inference晶片布局拆解:Groq LPU、HBSRAM與NVIDIA Inference戰略

摘要

2025年12月24日NVIDIA以200億美元實質掌控Groq的智慧財產權與團隊,看中其以軟體為主設計、以SRAM為核心記憶體的Groq LPU在極低延遲Inference的表現;此外,NVIDIA也於CES 2026強調記憶體容量成為AI Inference的新瓶頸。為突破記憶體瓶頸,預計 GPU-for-Everything的時代將邁向終結,而異質化記憶體階層的新典範將展開。未來Hybrid Bonded SRAM、HBF皆成為AI晶片設計的潛在選項,以突破HBM在頻寬、延遲、容量上的限制。因此本篇報告主要深度解析:(1) Inference晶片設計要求;(2) Groq LPU/GroqRack技術解析;(3) HBM vs. HBF vs. HBSRAM比較;(4) Groq LPU對NVIDIA的戰略意義。期能為廠商與投資人解析Inference晶片要求、Groq LPU和HBSRAM的技術發展與未來可能性。

一. Inference晶片設計要求

二. Groq LPU/GroqRack技術解析

三. HBM vs. HBF vs. HBSRAM

四. Groq LPU對NVIDIA的戰略意義

五. 拓墣觀點

圖一 Three Scaling Laws

圖二 NVIDIA於CES 2026強調Context Window Size為新瓶頸

圖三 2016~2024年Memory Wall

圖四 NVIDIA Inference Context Memory Storage Platform Tray

圖五 NVIDIA Inference Context Memory Storage Platform Rack

圖六 Groq LPU晶片架構

圖七 LPU序列處理與GPU比較

圖八 GroqWare軟體架構

圖九 GroqRack配置示意圖

圖十 Groq產品系列圖

圖十一 GroqChip/GroqNode Scale-Out拓樸

圖十二 記憶體階層與HBSRAM、HBM、HBF

圖十三 AMD 3D V-Cache堆疊示意圖

圖十四 AMD MI300堆疊示意圖

圖十五 SRAM單位元占用面積

圖十六 各類型AI晶片Inference適用性比較

圖十七 Cerebras WSE-3結構

圖十八 Cerebras WSE-3多層式板載封裝結構

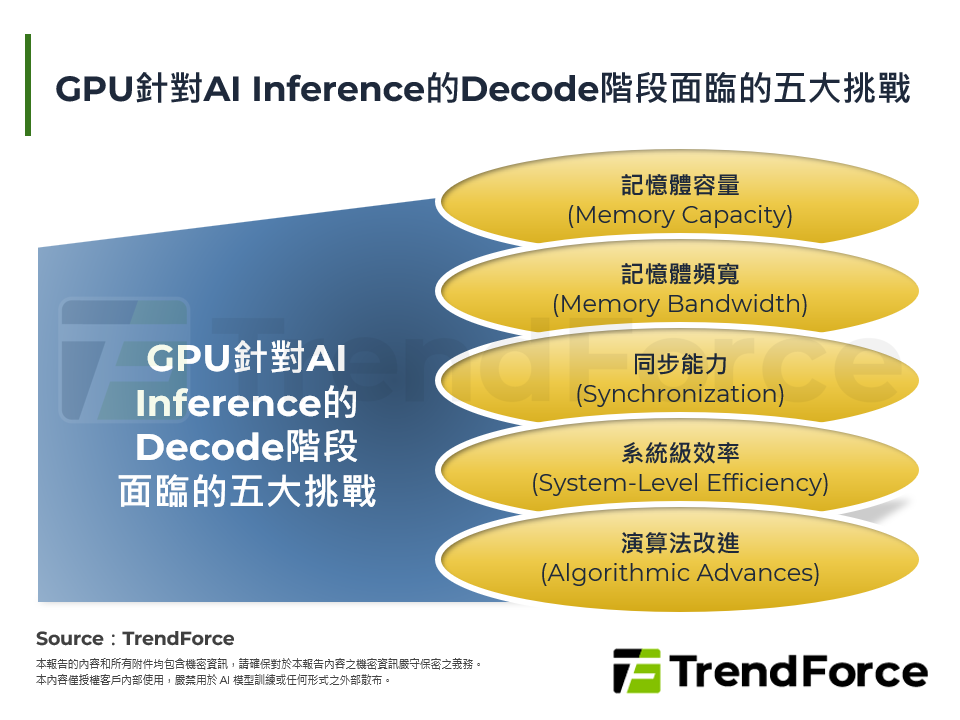

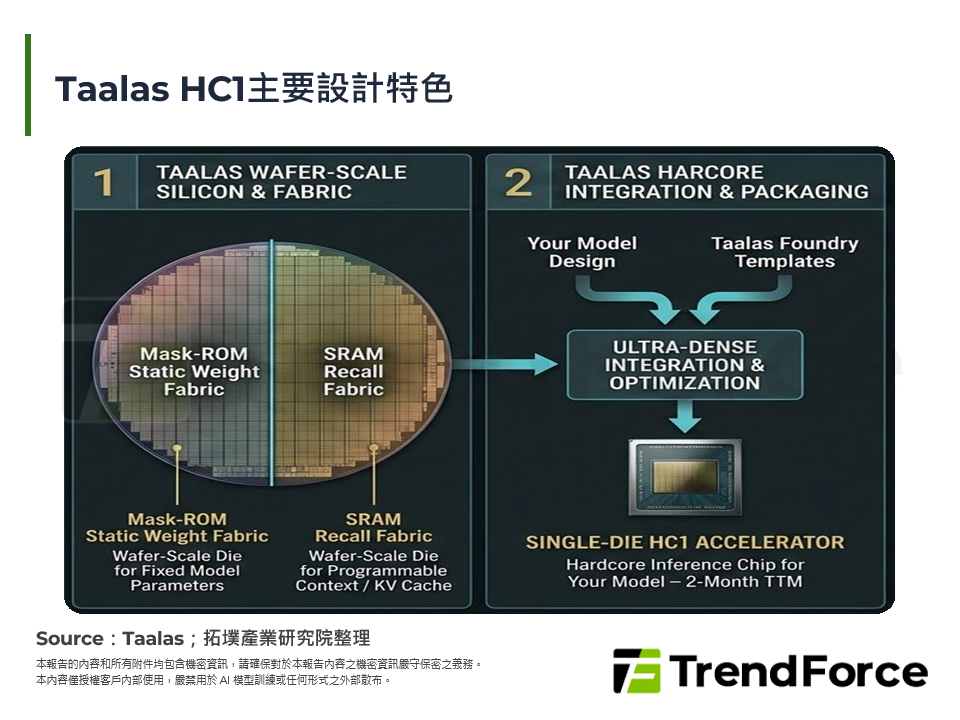

表一 Inference Decode階段性能的主要限制因素

表二 Prefill與Decode比較

表三 NVIDIA實測HBM、3D-DRAM、SRAM方案比較

表四 各類型處理器比較

表五 GPU、TPU、LPU比較

表六 NVIDIA新三層式記憶體架構

表七 Groq LPU、B200、TPU v7性價比分析

表八 各大AI晶片供應商Inference布局

表九 低延遲、高頻寬、低功耗AI晶片主要供應商