SOC的嶄新面貌---ESL工具推動軟硬體協同設計成真

摘要

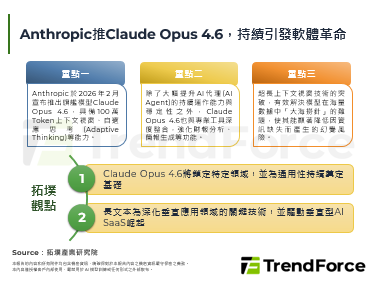

當晶片設計不斷地朝微縮尺寸發展,晶片的設計工作也快速改變中;從最原始的使用電路閘設計、進展到利用電腦輔助語言如Verilog與VHDL來提高設計的效率、一直到最近幾年流行的軟硬體協同設計,也就是ESL(Electronic System Level:電子系統層級)方式的EDA工具使用。ESL設計方式的IC設計將會日益重要,主要的原因在於內嵌式處理器的需求持續上升,而處理器的設計也逐漸向多核心邁進,另外日益昂貴的光罩成本,也促使IC設計公司必須尋求更有效率的方式,來確保所設計的IC產品正確無誤地被生產。ESL的設計觀念與設計工具仍在不斷地發展之中,本文將介紹主要的EDA廠商於ESL的產品現況與發展趨勢。

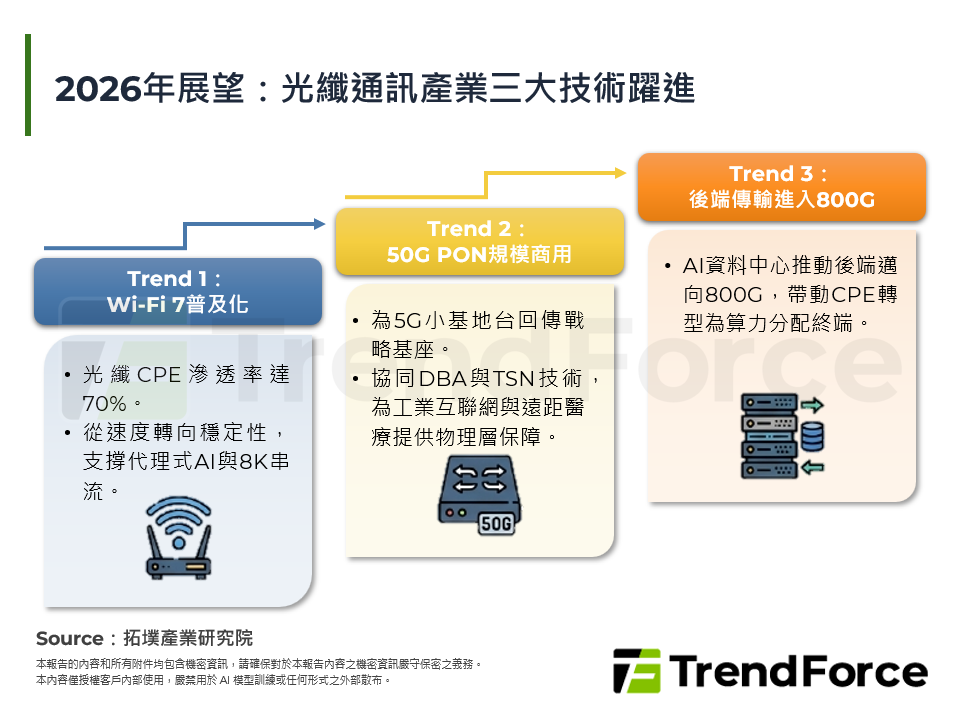

平行處理的軟硬體協同設計驗證流程圖

Source:Cadence;拓墣產業研究所整理,2005/06